#### **Binary Code Retrofitting and Hardening Using SGX**

#### Shuai Wang, <u>Wenhao Wang</u>, Qinkun Bao, Pei Wang, XiaoFeng Wang, and Dinghao Wu

The Pennsylvania State University, Indiana University Bloomington, Institute of Information Engineering

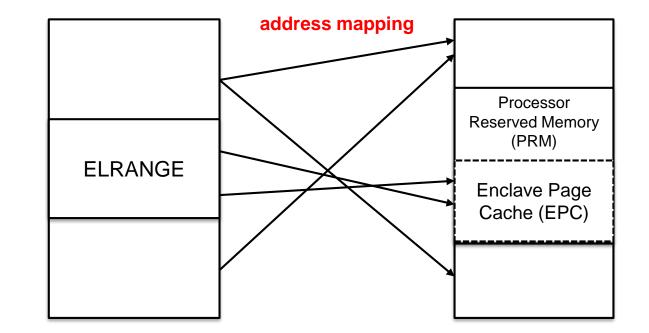

- Available in Intel Commercial CPUs

Hardware isolated memory regions

Protection under a strong adversary model

- □ A bit performance penalty (~10%)

- Available in Intel Commercial CPUs

Hardware isolated memory regions

Protection under a strong adversary model

- □ A bit performance penalty

Can binary code hardening benefit from SGX?

#### □ Graphene-SGX, Haven

Large TCB (53 kloc for Graphene-SGX)

#### Shielding applications from an untrusted cloud with Haven

Andrew Baumann Marcus Peinado Galen Hunt Microsoft Research

.

#### Abstract The current best practice for protecting secrets in the Generation of the second secon • Watch 22 🛨 Star 99 ¥ Fork 41 Today's cloud computing infrastruc tial trust. Cloud users rely on both t Code () Issues 27 () Pull requests 11 Projects 0 E Wiki II Insights its globally-distributed software/har Introduction to Intel SGX Support expose any of their private data. We introduce the notion of shiel chiache edited this page Jul 20, 2016 · 10 revisions protects the confidentiality and inteits data from the platform on which What is Intel SGX? Pages 11 operator's OS, VM and firmware). is the first system to achieve shiel SGX (Software Guard Extension) is a new feature of the latest Intel CPUs. According to https://github.com/ayeks/SGX-hardware, SGX is available in CPUs that are launched after October Basics modified legacy applications, inclu 1st, 2015. Apache, on a commodity OS (Wii Introduction to Graphene ity hardware. Haven leverages the 1 Intel SGX is designed to protection critical applications against potentially malicious system stack, Quick Start from the operating systems to hardware (CPU itself excluded). SGX creates a hardware encrypted Intel SGX to defend against privil Run Applications in Graphene memory region (so-called enclaves) from the protected applications, that neither compromised Manifest Syntax cal attacks such as memory probes, Implemented System Calls operating systems, nor hardware attack such as cold-boot attack can retrieve the application dual challenges of executing unmo secrets. Building Linux Kernel Support and protecting them from a malici Intel SGX Support motivated recent changes in the SG Why use Graphene Library OS for Intel SGX? Introduction to Intel SGX Support Porting applications to Intel SGX platform can be cumbersome. To secure an application with SGX, Ouick Start developers must recompile the application executable with the Intel SDK (Linux SDK: Run Applications with SGX https://github.com/01org/linux-sgx). Moreover, the secured applications have no access to any OS Manifest Syntax features, such as opening a file, creating a network connection, or cloning a thread. For any Debugging SGX Support interaction with the host, developers must define untrusted interfaces that the secure applications can call to leave the enclaves.

Graphene Library OS provides the OS features needed by the applications, right inside the SGX enclaves. To secure any applications, developers can directly load native, unmodified binaries into enclaves, with minimal porting efforts. Graphene Library OS provides signing tool to sign all binaries that are loaded into the enclaves, just like the Intel SGX SDK.

#### Developer's Guide

- Debugging Graphene

- PAL Host ABI

- Port Graphene PAL to Other

- Hosts

- □ Graphene-SGX, Haven

- Large TCB (53 kloc for Graphene-SGX)

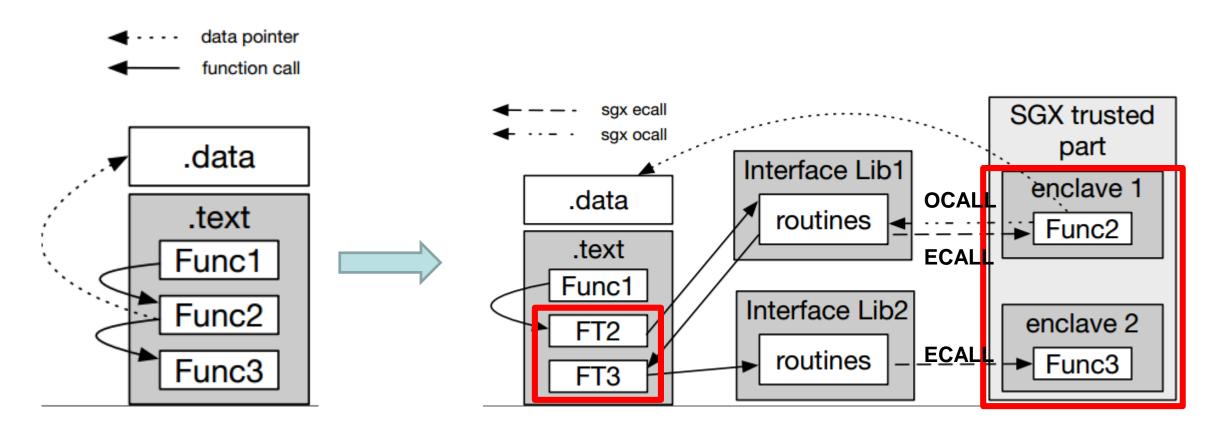

- Our solution

- Techniques to dissect binary code into multiple components

- Put into separated enclaves

#### Shielding applications from an untrusted cloud with Haven

Andrew Baumann Marcus Peinado Galen Hunt

Microsoft Research

#### Abstract The current best practice for protecting secrets in the Given Scarlab / graphene • Watch 22 🛨 Star 99 ¥ Fork 41 Today's cloud computing infrastruc tial trust. Cloud users rely on both t Code () Issues 27 () Pull requests 11 Projects 0 E Wiki II Insights its globally-distributed software/har Introduction to Intel SGX Support expose any of their private data. We introduce the notion of shiel chiache edited this page Jul 20, 2016 · 10 revisions protects the confidentiality and inteits data from the platform on which What is Intel SGX? Pages 11 operator's OS, VM and firmware). is the first system to achieve shiel SGX (Software Guard Extension) is a new feature of the latest Intel CPUs. According to https://github.com/ayeks/SGX-hardware, SGX is available in CPUs that are launched after October Basics modified legacy applications, inclu 1st, 2015. Apache, on a commodity OS (Wii Introduction to Graphene ity hardware. Haven leverages the h Intel SGX is designed to protection critical applications against potentially malicious system stack, Quick Start from the operating systems to hardware (CPU itself excluded). SGX creates a hardware encrypted Intel SGX to defend against privil Run Applications in Graphene memory region (so-called enclaves) from the protected applications, that neither compromised Manifest Syntax cal attacks such as memory probes, Implemented System Calls operating systems, nor hardware attack such as cold-boot attack can retrieve the application dual challenges of executing unmo secrets. Building Linux Kernel Support and protecting them from a malici Intel SGX Support motivated recent changes in the SG Why use Graphene Library OS for Intel SGX? Introduction to Intel SGX Support Porting applications to Intel SGX platform can be cumbersome. To secure an application with SGX, Ouick Start developers must recompile the application executable with the Intel SDK (Linux SDK: Run Applications with SGX https://github.com/01org/linux-sqx). Moreover, the secured applications have no access to any OS Manifest Syntax features, such as opening a file, creating a network connection, or cloning a thread. For any Debugging SGX Support

features, such as opening a file, creating a network connection, or cloning a thread. For any interaction with the host, developers must define untrusted interfaces that the secure applications can call to leave the enclaves.

Graphene Library OS provides the OS features needed by the applications, right inside the SGX enclaves. To secure any applications, developers can directly load native, unmodified binaries into enclaves, with minimal porting efforts. Graphene Library OS provides signing tool to sign all binaries that are loaded into the enclaves, just like the Intel SGX SDK.

| ٠ | Debugging Graphene         |  |  |  |

|---|----------------------------|--|--|--|

| ٠ | PAL Host ABI               |  |  |  |

| ٠ | Port Graphene PAL to Other |  |  |  |

**Developer's Guide**

Hosts

#### □ Two capabilities

- change in enclave memory access semantics

- protection of the address mappings of the application

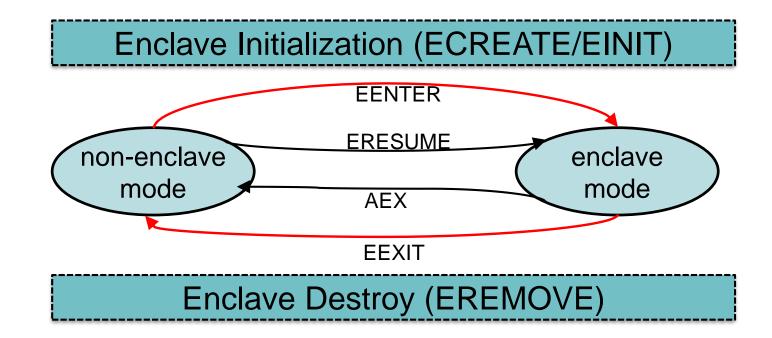

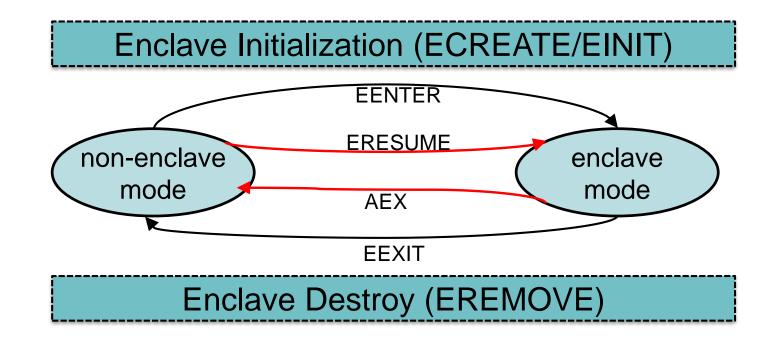

#### □ Life cycle

#### □ Life cycle

- □ Controlled enclave entry

- □ Separated stack

- CPU state and registers are cleared if exceptions occur inside the enclaves.

| 92  | /*                                                                            |

|-----|-------------------------------------------------------------------------------|

| 93  | *                                                                             |

| 94  | * Function: enclave_entry                                                     |

| 95  | * The entry point of the enclave.                                             |

| 96  | *                                                                             |

| 97  | * Registers:                                                                  |

| 98  | * XAX - TCS.CSSA                                                              |

| 99  | <ul> <li>XBX - the address of a TCS</li> </ul>                                |

| 100 | <ul> <li>XCX - the address of the instruction following the EENTER</li> </ul> |

| 101 | <ul> <li>XDI - the reason of entering the enclave</li> </ul>                  |

| 102 | <ul> <li>XSI - the pointer to the marshalling structure</li> </ul>            |

| 103 | */                                                                            |

| 104 | DECLARE_GLOBAL_FUNC enclave_entry                                             |

| 105 | /*                                                                            |

| 106 | *                                                                             |

| 107 | * Dispatch code according to CSSA and the reason of EENTER                    |

| 108 | <pre>* eax &gt; 0 - exception handler</pre>                                   |

| 109 | <pre>* edi &gt;= 0 - ecall</pre>                                              |

| 110 | <pre>* edi == -1 - do_init_enclave</pre>                                      |

| 111 | * edi == -2 - oret                                                            |

| 112 | * Registers                                                                   |

| 113 | <ul> <li>No need to use any register during the dipatch</li> </ul>            |

| 114 | *                                                                             |

| 115 | */                                                                            |

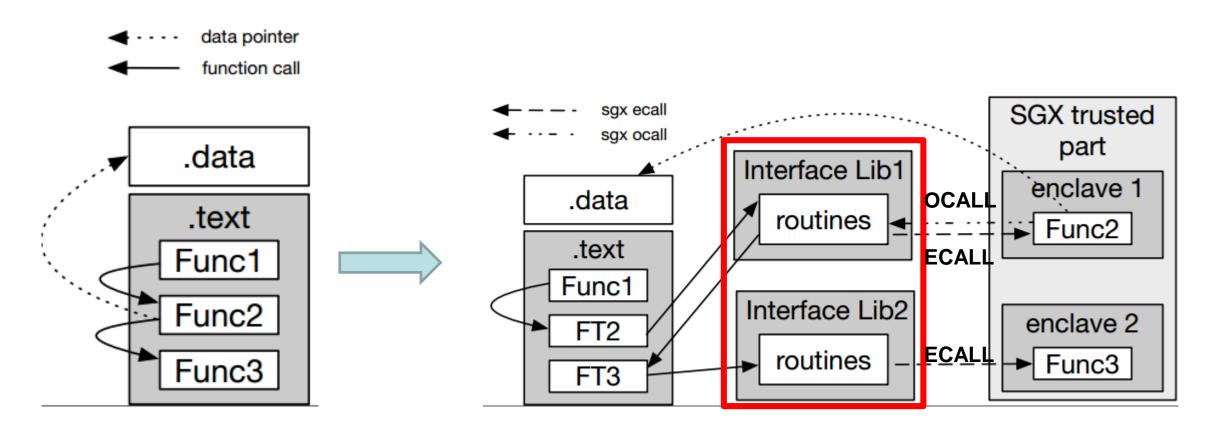

## Methodology

# Methodology

Interface library: maintain routine code for ecall and ocall

# Methodology

In-place binary editing: Trampoline code

## Challenges

Binary code reassembly disassembling

- > Uroboros

- □ How to generate enclave libraries

- Intel SGX SDK

- **D** Binary instrumentation to jump to the enclave entry

- Trampoline code

- Exceptions

- Customized exception handling inside the enclaves

## Challenges

Binary code reassembly disassembling

- > Uroboros

- □ How to generate enclave libraries

- Intel SGX SDK

- **D** Binary instrumentation to jump to the enclave entry

- Trampoline code

- Exceptions

- Customized exception handling inside the enclaves

## Some technique details

#### □ In-place binary editing

> Trampoline code

| 1  | trampoline_foo: |                                     |  |  |

|----|-----------------|-------------------------------------|--|--|

| 2  | push            | % <b>rbp</b>                        |  |  |

| 3  | mov             | %rsp,%rbp                           |  |  |

| 4  | push            | <pre>\$return_addr</pre>            |  |  |

| 5  | push            | %rax                                |  |  |

| 6  | mov             | <pre>\$sgx_interface_foo,%rax</pre> |  |  |

| 7  | xchg            | %rax,(%rsp)                         |  |  |

| 8  | ret             |                                     |  |  |

| 9  | рор             | % <b>rbp</b>                        |  |  |

| 10 | ret             |                                     |  |  |

## Some technique details

#### Exceptions

Customized exception handling inside the enclaves

| 1  | exception_exit: |                                  |  |  |

|----|-----------------|----------------------------------|--|--|

| 2  | mov             | % <b>gs</b> :0x0,% <b>rax</b>    |  |  |

| 3  | mov             | %rax,%rbx                        |  |  |

| 4  | call            | update_ocall_lastsp              |  |  |

| 5  | mov             | 0x20(% <b>rbx</b> ),% <b>rdx</b> |  |  |

| 6  | mov             | 0×98(% <b>rdx</b> ),% <b>rbp</b> |  |  |

| 7  | mov             | 0×90(% <b>rdx</b> ),% <b>rsp</b> |  |  |

| 8  | mov             | \$target_addr,% <b>rbx</b>       |  |  |

| 9  | mov             | \$EEXIT, % <b>rax</b>            |  |  |

| 10 | enclu           |                                  |  |  |

## **Proof-of-concept implementation**

□ Extend Uroboros with SGX instrumentation functionalities.

- Employ the core functionality of Uroboros to identify program relocation symbols (e.g., code pointers).

- Use industrial standard reverse engineering tool (IDA-Pro) to recover the function type information.

- Implement the instrumentation functionality in Scala, with over 1,700 LOC.

- The proof-of-concept implementation of the exception handling mechanism adds 56 lines of C code.

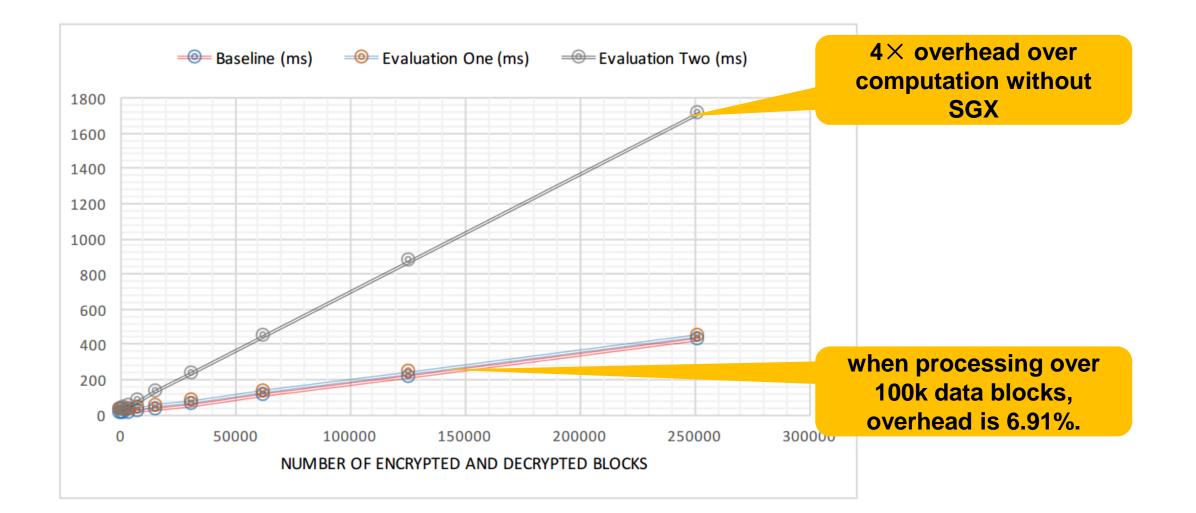

#### **Evaluation**

- Evaluations mainly focus on understanding the feasibility and cost of the instrumentation products.

- Two major factors would contribute to the performance penalty of the SGX protected code:

- Execution slowdown of code components inside enclaves.

- Cross-enclave control flow transfers, e.g., enclave ECALL.

## **Evaluation Setup**

- Our preliminary evaluation instruments sensitive procedures provided by cryptographic libraries.

- AES implementation in OpenSSL (version 0.9.7)

- Write sample code to trigger the encryption and decryption functions in the library.

- > key length is set as 256.

- > AES electronic codebook (ECB) mode.

## **Evaluation Setup**

|                | Functions                                           |

|----------------|-----------------------------------------------------|

| Evaluation One | AES_decrypt, AES_encrypt, AES_ecb_encrypt, enc, dec |

| Evaluation Two | AES_decrypt, AES_encrypt                            |

#### To measure the performance cost of code within enclave (first factor):

- All encryption/decryption computations are performed within one enclave.

- Pointers on key and data blocks are passed in through the interface.

## **Evaluation Setup**

|                       | Functions                                           |

|-----------------------|-----------------------------------------------------|

| <b>Evaluation One</b> | AES_decrypt, AES_encrypt, AES_ecb_encrypt, enc, dec |

| Evaluation Two        | AES_decrypt, AES_encrypt                            |

# To measure the impact of inter-enclave control flow transfers (second factor):

- Put the **block-level** encryption/decryption functions into the enclave.

- Control the number of inter-enclave control transfers by changing the length of the input data.

#### **Evaluation Results**

#### **Evaluation Results**

| Case                  | Input Bin (KB) | Output Bin (KB) | Interface Libs (KB) | Enclaves (KB) | Output Total (KB) |

|-----------------------|----------------|-----------------|---------------------|---------------|-------------------|

| Evaluation One        | 48             | 48              | 16                  | 116           | 180               |

| <b>Evaluation Two</b> | 48             | 48              | 12                  | 108           | 168               |

#### We measure the size increase in terms of multiple components:

- Size of output binary is identical with the input, since we perform inplace binary instrumentation.

- Both SDK routines and our routine code introduce size increase.

- The overall size increase is within a reasonable extent.

- Evaluation One has three more functions than Evaluation Two.

#### **Future works**

#### Limitations

$\succ$

. . .

- How to reliably recover the function prototype?

- > How to deal with the shared variables among several isolated enclaves?

- > Some instructions/operations may not be supported inside the enclaves.

#### Thanks! Contact: <u>ww31@indiana.edu</u>